Notice

Modèles mémoire pour les multiprocesseurs à mémoire partagée

- document 1 document 2 document 3

- niveau 1 niveau 2 niveau 3

Descriptif

La plupart des systèmes qui s'apparentent à des ordinateurs un tant soit peu sophistiqués comprennent plusieurs unités de calcul qui communiquent par l'intermédiaire d'une mémoire partagée.

La programmation de ces systèmes est notoirement difficile, en raison de l'explosion de l'espace des états possibles du système. Mais il existe une autre difficulté : ces systèmes ne suivent pas le modèle simple de fils d'exécution exécutant chacun à leur tour des instructions dans l'ordre du programme et agissant instantanément sur la mémoire commune. Cette situation résulte des optimisations matérielles, telles que l'exécution *out-of-order* et spéculative, ainsi que de la présence de tampons et de caches destinés à ne pas contraindre les coeurs d'exécution à avancer au rythme de la mémoire. Ces optimisations matérielles ne changent pas le modèle d'exécution séquentielle, mais deviennent visibles des programmes parallèles.

L'exposé portera sur la définition de modèles rigoureux et précis du comportement des machines multiprocesseurs, un préalable nécessaire pour l'écriture de compilateurs, d'outils d'analyse et d'idiome de programmation *lock-free* pour la programmation parallèle. Nous confrontons systématiquement nos modèles aux machines effectivement disponibles. Cette démarche aboutit à la proposition de modèles crédibles et expérimentalement vérifiés pour les machines à base de processeurs Intel x86, IBM Power et ARM. À l'occasion nous avons trouvé quelques bugs dans les implantations matérielles de ces architectures.

Intervention / Responsable scientifique

Dans la même collection

-

Explorations Mathématiques de l'activité du cerveau

TouboulJonathanExplorations Mathématiques de l'activité du cerveau Le siècle dernier a été une période fascinante durant laquelle les recherches expérimentales ont fait des avancées majeures sur la

-

Logic-based static analysis for the verification of programs with dynamically allocated data struct…

DrăgoiCezaraSoftware development has reached a complexity level that cannot be handled without the aid of computer assisted methods. It is therefore of the highest importance to have rigorous methods and

-

Resolving Entities in the Web of Data

ChristophidesVassilisOver the past decade, numerous knowledge bases (KBs) have been built to power a new generation of Web applications that provide entity-centric search and recommendation services. These KBs offer

-

Wireless In the Woods: Monitoring the Snow Melt Process in the Sierra Nevada

WatteyneThomasHistorically, the study of mountain hydrology and the water cycle has been largely observational, with meteorological forcing and hydrological variables extrapolated from a few infrequent manual

-

Phénomènes Aléatoires dans les Réseaux

RobertPhilippeLes phénomènes aléatoires sont une composante-clé des réseaux de communication, ils interviennent, de façon majeure, dans le trafic que les réseaux traitent, ainsi que dans certains algorithmes

-

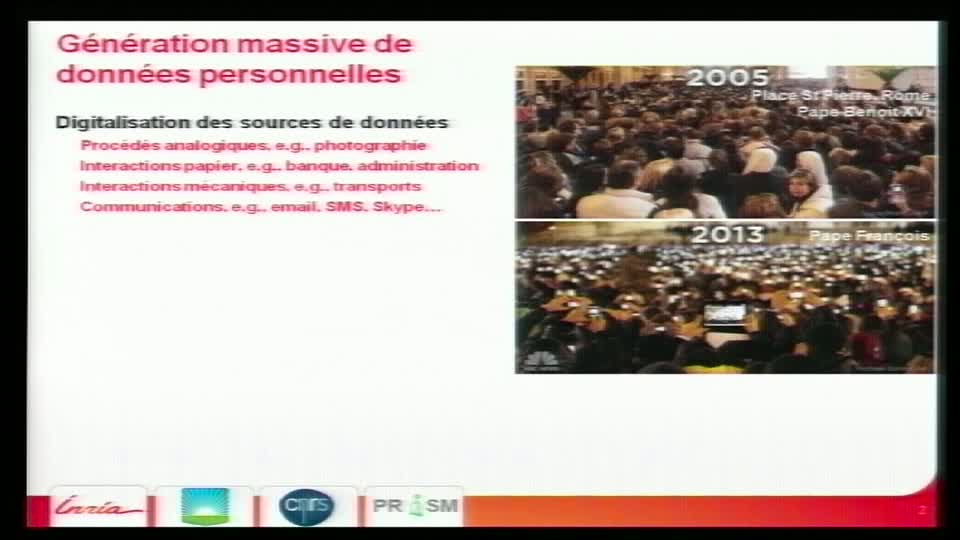

Gestion de données personnelles respectueuse de la vie privée

AnciauxNicolasEn très peu de temps, nous sommes entrés dans une ère de génération massive des données personnelles créées par les individus, leurs équipements digitaux ou mises à disposition par certaines

-

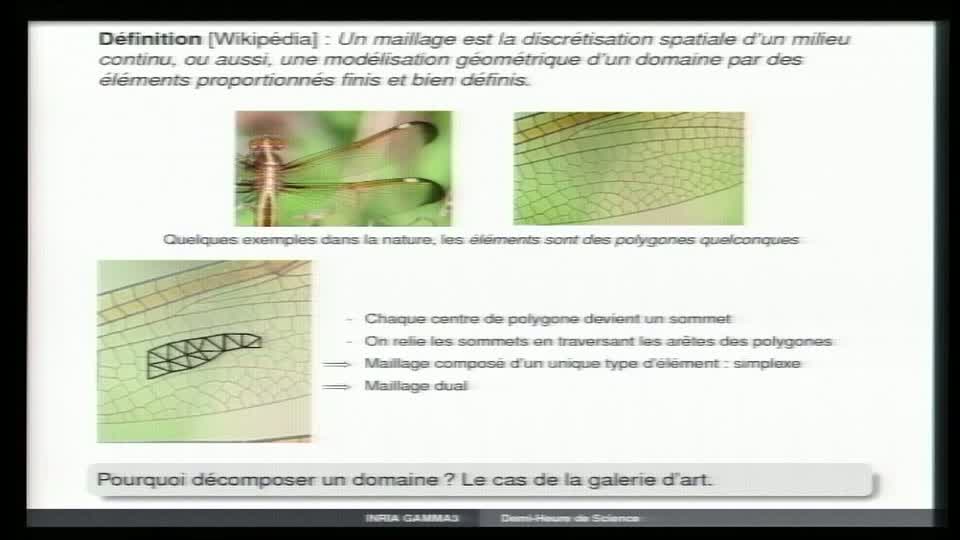

Génération de maillages pour la simulation numérique

LoseilleAdrienUne branche importante du calcul scientifique consiste à simuler sur ordinateurs des phénomènes physiques complexes. Son intérêt consiste à mieux appréhender des problèmes fondamentaux : solution

-

Réduction de modèles de voies de signalisation intracellulaire

FeretJérômeLes voies de signalisation intracellulaire sont des cascades d'interaction entre protéines, qui permettent à la cellule de recevoir des signaux, de les propager jusqu'à son noyau, puis de les

-

Réseau optiques, algorithmes et probabilités

RobertsJ. B.L'objectif des recherches de l'équipe RAP est de modéliser le comportement de réseaux de divers types, soumis à une demande de nature aléatoire, afin la prédire leurs performances. Le partage des